Gallery

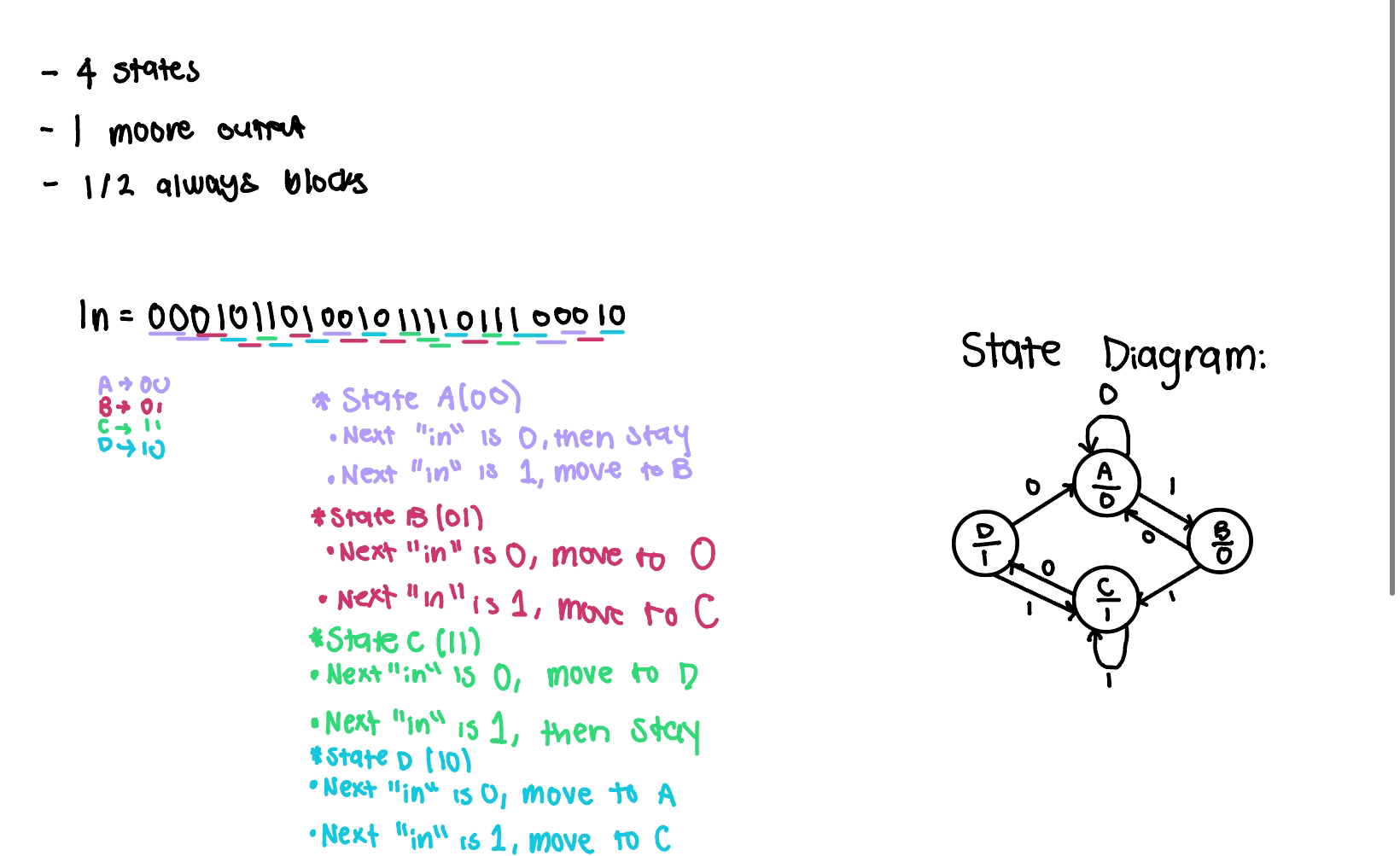

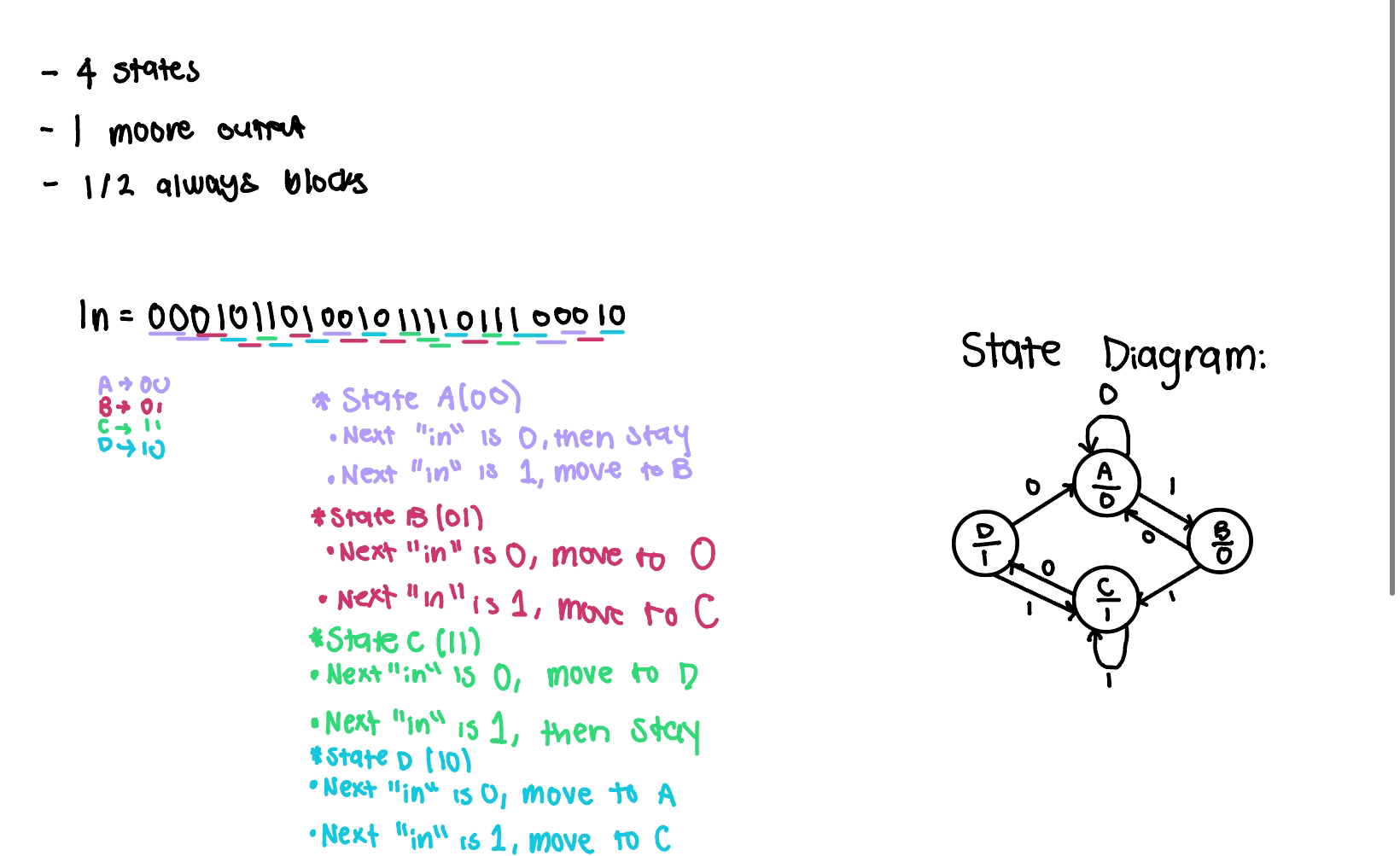

State flow ensuring spikes don’t toggle output.

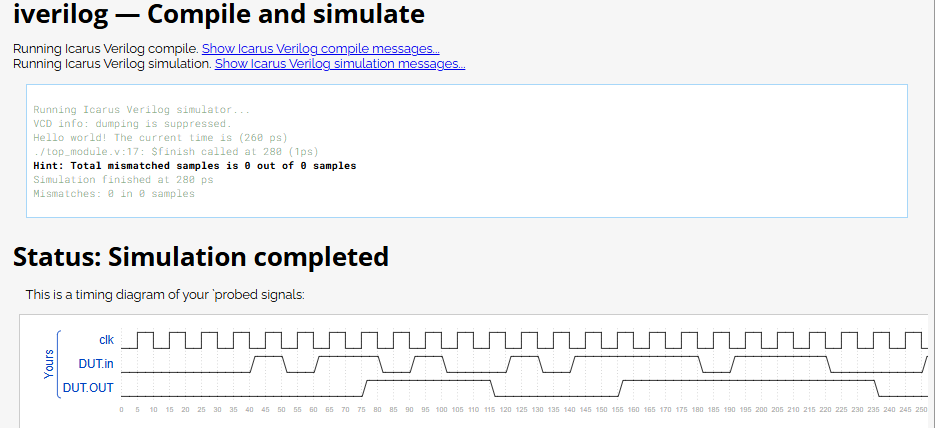

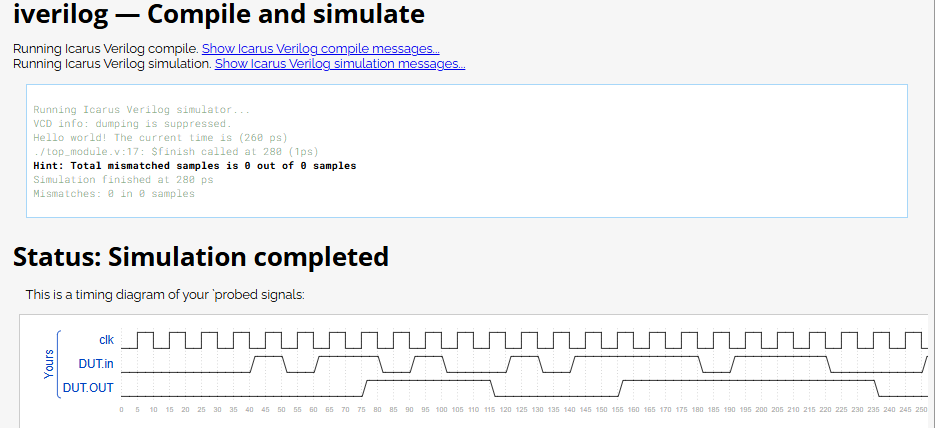

Single-cycle glitches suppressed; valid edges pass.

FSM + Verilog filter that rejects single-cycle glitches and stabilizes the measured signal.

This design suppresses brief high/low spikes (≤ 1 clock) using a four-state Moore FSM implemented in Verilog, producing a clean, debounced output suitable for downstream logic. It was validated with a targeted stimulus sequence and waveform inspection.

always blocks.View the Verilog implementation and simulation:

Open HDLBits Demo →

State flow ensuring spikes don’t toggle output.

Single-cycle glitches suppressed; valid edges pass.